Processor’s approach to provisioning shared peripherals and resources – Flynn Embedded

In a multi-core heterogeneous CPU, multiple cores are like multiple brains, and peripherals and memory resources are like hands and feet, so how should multiple brains control hands and feet to ensure their normal and orderly operation?

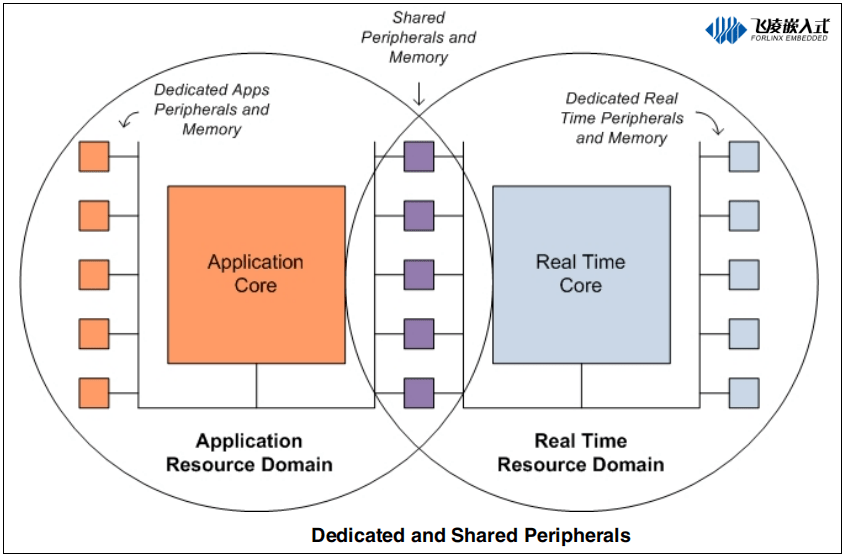

Take NXP i.MX8M Plus processor’s A-core and M-core as an example, in fact, only a small number of peripherals are assigned to which core, while most of them can be used by both A-core and M-core. As shown in the figure below.

Here we demonstrate by UART3 on FeiLing embedded OKMX8MP-C development board, and write A-core and M-core programs to control UART3 to print information at the same time, and link the development board with PC through UART3, you can see A-core and M-core output information at the same time in PC serial debug interface.

So in the actual application, when a peripheral needs to be exclusive by the specified core or used by multiple cores at the same time, how to arrange the timing reasonably to avoid peripheral output exceptions? Next, I will take Feiling embedded OKMX8MP-C development board as an example to introduce the multi-core heterogeneous processor to the shared peripherals and resources of the deployment method to everyone.

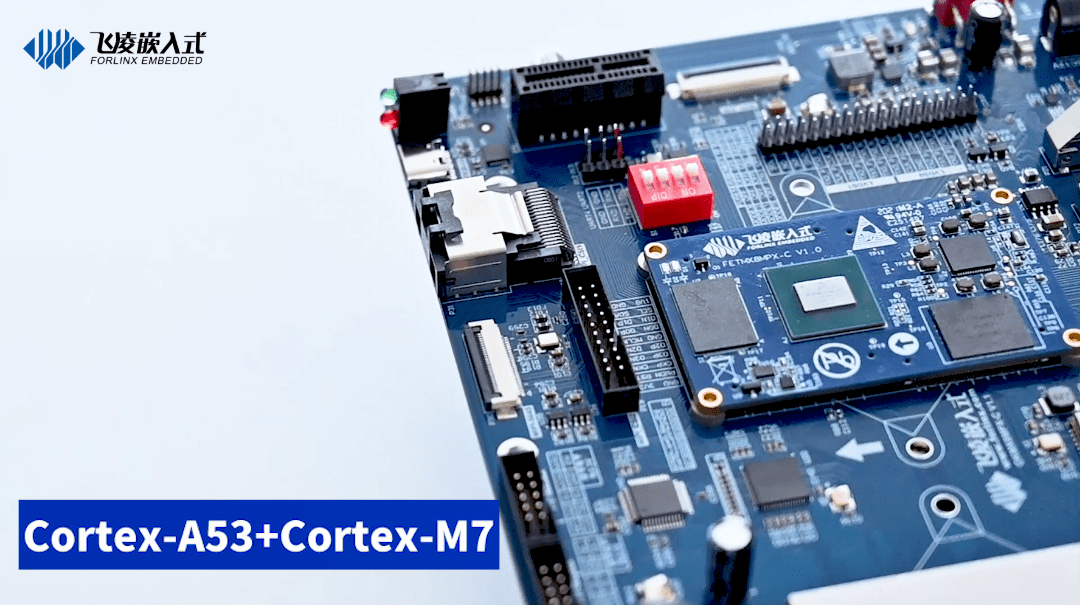

The NXP i.MX8M Plus processor on Fibridge’s embedded OKMX8MP-C development board is equipped with powerful performance, integrating four Arm Cortex-A53 multitasking cores up to 1.8GHz (1.6GHz for industrial grade) and one Cortex-M7 real-time core, which can handle both high-speed data throughput and processing, as well as complex human-machine interface processing, it can handle them all with ease.

1, A-core exclusive peripherals

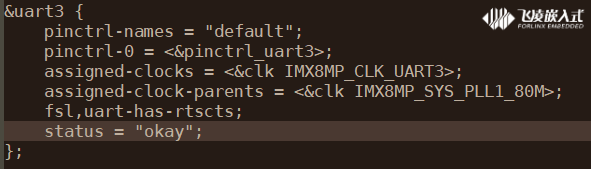

This case is relatively simple, define the device node in the device tree, compile the new device tree and copy the generated OK8MP-C.dtb and Image to the following directory.

development-board/run/media/mmcblk2p1/

Reboot the development board, while the M-core program just does not initialize UART3. Take UART3 as an example.

2, M-core exclusive peripherals

For the NXP i.MX8M Plus processor, since both A and M cores have shared and equal access to memory and peripherals, access to assigned memory and peripherals is protected at the hardware level through the resource domains controller to ensure that no resource conflicts arise.

The i.MX8M Plus processor allows for the definition of up to four resource domains and the assignment of different memory and peripheral resources to these resource domains. By default, the A-core and associated peripherals are assigned to domain 0; when the M-core program is run, the M-core and associated peripherals are also initially in domain 0, but are immediately reassigned to domain 1.

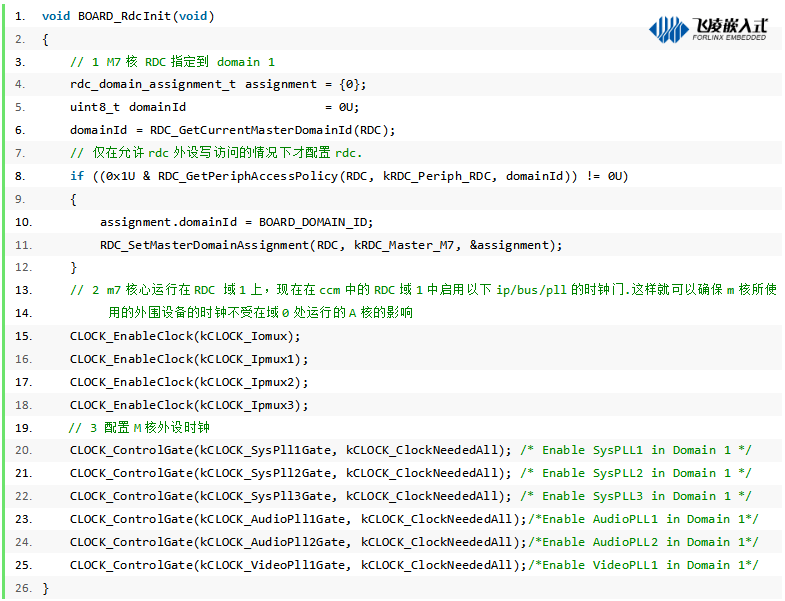

Therefore, if a peripheral needs to be used by the M7 kernel alone, first, the A-core device tree must be modified to remove the peripheral node; second, domain 0 must be changed to domain 1 in the M-core program; and finally, the peripheral must be initialized so that it can be controlled separately. The domain conversion code is as follows.

3、Multi-core shared peripherals

If multiple cores want to share a peripheral but need to be exclusive at some time and release it later, or if the developers of multiple cores are not the same person and want to force exclusive use of a core in their own program to avoid errors, is it possible to achieve this?

The answer is yes – use the RDC function, which is a Resource Domain Controller, and it can achieve the exclusive use and release of a certain peripheral through both registers and semaphores.

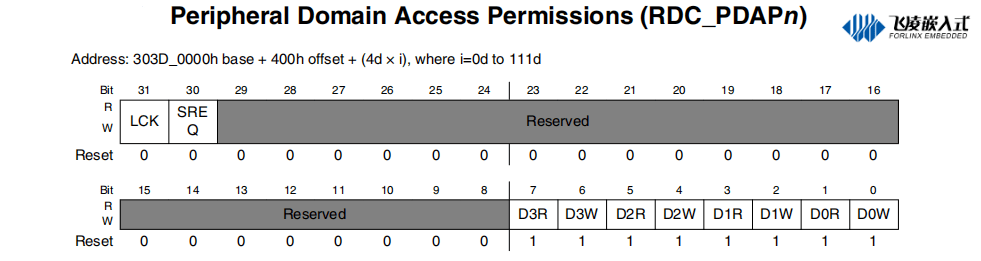

1) Register RDC_PDAPn

Since the i.MX8M Plus processor supports up to 4 domains, writing different values to the last 8 bits of the register will allow the corresponding domain to enable reading and writing to a certain pin and memory, for example, to prohibit A-core domain 0 from reading and writing to a certain pin, set the register to 0xFC, the last two bits are 0, which means that domain 0 is prohibited from reading and writing to this device; the other six bits are 1, which means that domain 1 to domain 3 are allowed to read and write to this device. The other six bits are 1, which means read and write from domain 1 to 3 is allowed.

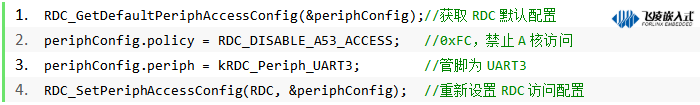

Each shared peripheral has a serial number in the RDC resource table, which is used to distinguish other peripherals, for example, UART3 is defined in RDC as follows

kRDC_Periph_UART3 = 104U, /**< UART3 RDC Peripheral */

In the M-core program, you can modify the program as follows to achieve the purpose of UART3 exclusive to M-core.

Modify the program to verify that only the M core controls UART3 printing information at this time

Caution.

Because UART3 is not deleted in the device tree, when A-core starts the kernel to parse the device tree to generate the device file, it needs to operate on UART3. Since the M-core program forbids the A-core to access UART3, the kernel will not start normally at this time. You can add 10 seconds delay to wait for the kernel to finish booting, or you can tell the M-core to start RDC peripheral exclusive through dual-core communication after the A-core starts.

(1) Signal quantity RDCSEMA42

RDC SEMA42 is a semaphore that specifically works with the RDC function. When a domain acquires the SEMA42 lock for a peripheral, other domains will not be able to access this peripheral and can only wait for the domain to release the lock for that peripheral before they can access it again.

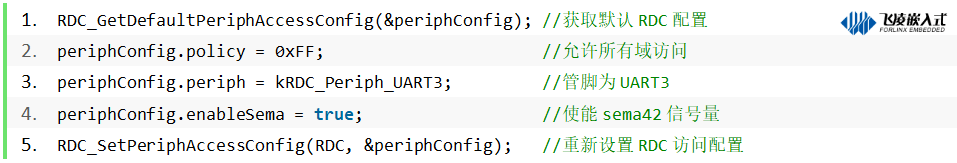

The RDC SEMA42 data lock is enabled and configured as follows.

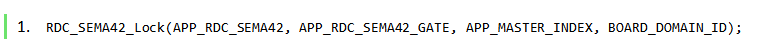

M-core locks on UART3 to gain access to the pin.

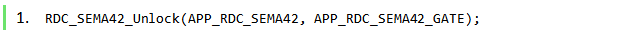

The M-core releases the RDC SEMA42 lock on UART3 and relinquishes the use of the pin.

After modifying the program and verifying, I found that, like the RDC register, the M-core gets the right to use UART3 after locking and can only send alone, the A-core will get an error to access UART3. After releasing the SEMA42 lock, both A-core and M-core can access UART3 now.

The above is how to use peripheral and memory resources for multi-core heterogeneous processors based on OKMX8MP-C development board, all engineer partners can set the strategy flexibly according to their needs to meet the needs of different scenarios.