RIS-V architecture commercial edge AI chip

RISC-V is an open source instruction set architecture (ISA) based on the principles of the Reduced Instruction Set (RISC). 2010, the open source instruction set architecture RISC-V first appeared at the University of California, Berkeley, and its open source architecture format soon attracted major vendors including IBM, NXP, WeaternDigital, NVIDIA, Qualcomm, Samsung, Google, Huawei, and Tesla. Samsung, Google, Huawei, Tesla, and other major vendors joined.

Unlike the mainstream mainstream architecture for x86 and ARM architecture, its characteristics are completely open source – since the beginning of the design, RISC-V instruction set architecture has a simple and efficient, open source open characteristics, can be used freely for any purpose, allowing anyone to design, manufacture and sell RISC-V chips and software.

While this was not the first open source instruction set, it is significant because its design makes it suitable for modern computing devices (such as warehouse-scale cloud computers, high-end cell phones, and embedded systems). The designers have taken into account performance and power efficiency in these uses. The instruction set also features a multitude of supported software, which addresses the usual weaknesses of new instruction sets.

As a new generation of streamlined instruction set, RISC-V is expected in the AIoT era, and the RISC-V ecosystem is gradually taking shape as new RISC-V companies and existing technology giants at home and abroad have laid out their positions. Under the influence of global “core shortage wave”, the trend of domestic MCU development and application is promising.

Founded in 2013, CAN (NASDAQ:CAN) is a technology company with ASIC high-performance computing chip design as its core, integrating chip development, computing device production and software services. As an early adopter of open source instruction set architecture for chip development in China, Canan Technology released the world’s first commercial edge AI chip with RISC-V architecture in 2018 to explore the maximum potential of AISC technology in the field of high performance computing and artificial intelligence.

Currently, Kanan Technology independently develops two generations of visual neural network gas pedal IP cores, and Kanchi series AI chips have products landed in smart home, smart access control, STEAM education, robotics and other scenarios.

Customers can purchase K510 core module and K510 CRB KIT V1.2 customer reference kit of Kanan Technology online through the official website of Huaqiu Mall at www.hqchip.com.

It is reported that Kanchi K510 launched by Jia Nan is the world’s first Linux-based Risc-V core high-precision AI processor.

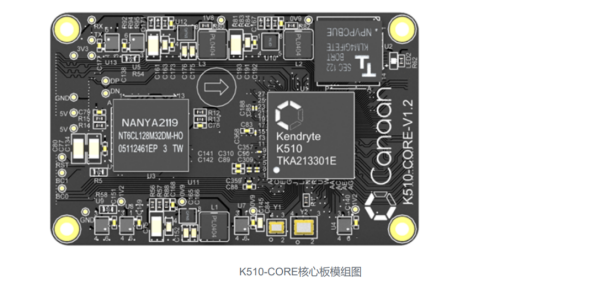

The K510-CORE is a core module with a K510 chip on board. The CPU is a dual-core 64bit RISC-V architecture, and the K510 is equipped with the second generation of self-developed neural network processor KPU2.0, which uses original computational data flow technology to increase computing power by 3 times compared to the previous generation while reducing power consumption. The onboard memory is 512MB LPDDR3@1600MHz, supporting two MIPI serial image inputs and one DVP parallel image input, and one MIPI image output.

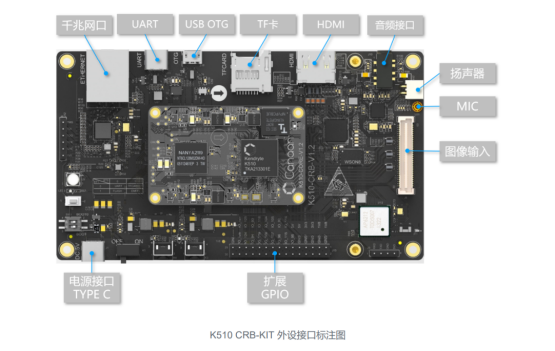

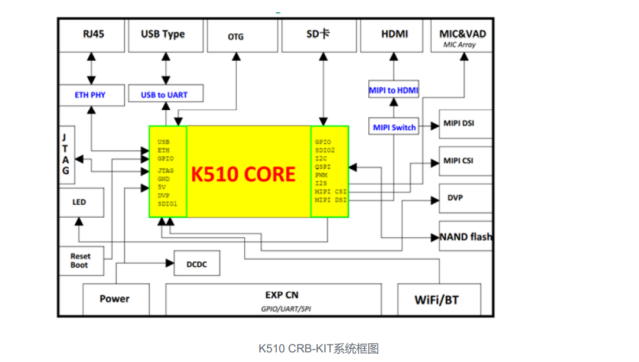

K510 CRB-KIT is a developer kit developed based on K510 chip, which adopts a hierarchical design and is based on K510 core module with rich peripherals for easy expansion. It supports high-speed communication interfaces such as USB 2.0 OTG+PHY, Gigabit Ethernet port, 3xSDIO and 3xSPI, and low-speed communication interfaces such as 4xUART, GPIO, I2C and I2S. Easy to use, informative, and able to help customers quickly realize creative evaluation, product prototype verification, and shorten product design cycle.

The K510 CRB-KIT is a complete user development kit that includes.

1 base board with a complete peripheral interface.

Also on board with 1 K510 core module (product model: K510-CORE-V1.2)

1 set of acrylic protective shell

1 camera daughter board (default configuration product model: K510-CRB-CAM_BOARD_IMX219_V1.2)

1 display daughter board (default configuration product model: K510-CRB-DISPLAY-V1.2-A.1)

2 x USB to typeC cable, 1 x micro USB OTG cable

Assembled with shell size: 100x160x25mm

Chip Features

Open source instruction set: 64-bit dual-core Risc-V CPU @800MHz, support Risc-V P extension, full Linux support

High-precision surging arithmetic power: equipped with second-generation self-developed KPU, peak arithmetic power of 2.45TFLOPS, supporting INT8 and BF16 data precision

HD triple camera processing: dual MIPI CSI + single DVP, 3D ISP support depth camera TOF Sensor

Rich framework: support TensorFlow, TFLite, ONNX, PyTorch, Caffe and other model import

Comprehensive open source: complete hardware design guide, open SDK and dozens of algorithm reference use cases

Application Scenarios

Industrial / professional cameras

Typical use case: Industrial inspection vision module

High frame rate image input

Sufficient computing power for image processing

3D recognition module

Typical use case: People counting camera

Multi-directional high-definition input

Deep information calculation to improve accuracy

Office consumer smart hardware

Typical use case: Attendance access control door lock intelligent terminal

Multi-eye live detection

HD screen display

STEAM intelligent education

Typical use case: AI education development board/robot

Flexible and easy-to-use tool chain

Full Linux support and continuous open source ecology

Rich examples, open community

Related posts:

- Application of Multi-Card Aggregation Multi-Link Aggregation Routing in Fire Fighting Intelligent Command System

- Low-cost ESP32 solution to support OpenHarmony system development (with 10+ sample project demos)

- Integrated three-phase bridge drive microcontroller – AiP8F7201

- STM32CUBEMX(5) – Custom IR NEC decoding, timer TIM capture method