Port parameters and internal module parameters

So in verlog, try to set it to parameter where there is a possibility of data change, so that it will not be changed from scratch again later.

The parameter is often used to define the data bit width, define the time delay, and change the referenced module by passing the parameter when the module and instance are referenced. Therefore, we try to set all the parameters that may change at the top level to make it clear at a glance and easy to maintain later.

Port parameters and internal module parameters

Definitions valid within this module that can be used for parameter passing.

If parameter passing is not possible when defined within the module, the

Parameter passing

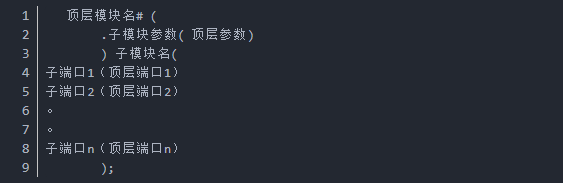

Parameter passing is often used for top-level parameters to be passed to submodules, so that we only need to focus on the content of the top-level entity and treat the content of the submodule as a black box, which is also very practical.

You can see that parameter passing and instantiation are very similar to each other.

The difference between parameter, define and localparam

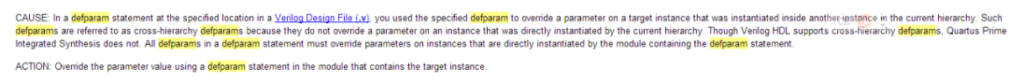

Defparam

defparam this separate out to say, in fact, this parameter, personally, I do not think the significance, because you use parameter parameter instantiation can be a good solution to the problem, defparam used to redefine the number of parameters, you can pass

defparam top level . submodule name 1. submodule name 2 = XXX

Such a syntax format change, so as to achieve specifically for a particular submodule change, which helps to instantiate a number of the same submodule, but I only change a submodule of the problem.!

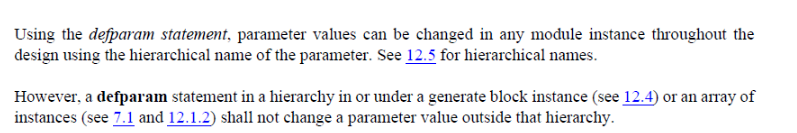

Let’s look together at the official documentation IEEE verilog 2005

defparam syntax we’ll go through the official syntax ourselves! This way you can have the takeaway.

This paragraph says that defparam applies to changing parameters under the specified hierarchical module and does not affect the parameters of other modules.

This paragraph also shows again that even modules generated using the same submodule instantiation are not affected and defparam is only for parameter changes under the specified path.

Defparam is currently not supported by all synthesis tools for synthesis, so it is only used for simulation.