That said, there are only three editors in this world, Vim, Emacs and other editors, of which Vim is called the god of editors, Emacs is called the editor of its god, of course, other editors can only ever be other editors.

Vim is the best text editor!

The learning curve of the major editors

For writing Verilog plug-ins, this number has also recommended two before. The first is a plug-in derived from Emacs.

The verilog-mode developer website is here, more content to go online. https://www.veripool.org/wiki/verilog-mode

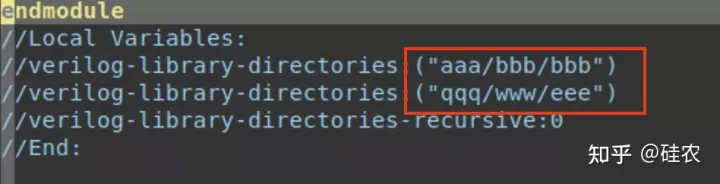

But this plug-in can not cross-folder.

Then I found another one, a plug-in on the official vim website, with a good autodefine function, you can write code without caring about the definition of reg and wire types at all, write assign and always blocks directly, and autodefine them at the end.

https://www.vim.org/scripts/script.php?script_id=4067

But this plug-in can not cross-folder.

So the blogger I sprouted, write their own to fully meet their needs, gVim plug-in! (There are echoes here ~) silicon farmer: your little python level, no B number in mind? Za heart, but, stepping through the iron shoes finally I found a collection of the above two plug-ins all the advantages of a gVim plug-in. I would like to call it the strongest open source gVim writing Verilog plug-in I’ve ever seen.

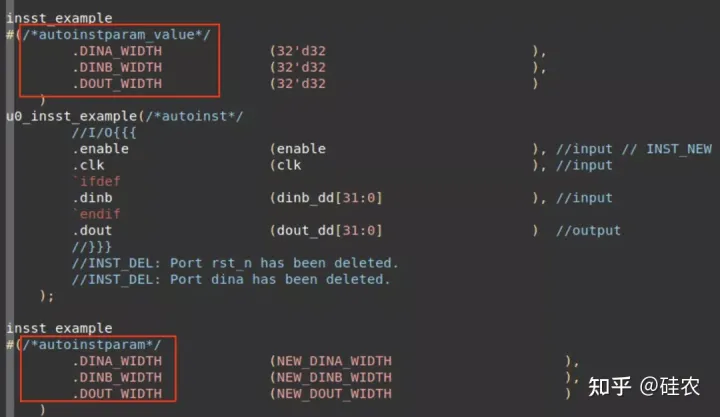

autoinst automatic instantiation

Support arbitrary cross-folder instantiation

support for automatic instantiation `ifdef any way to write, are you instantiated in

support for modifying the port modified to retain the port description syntax to support Verilog1995 and Verilog2001 support for instantiating the module port modified , the comments which were modified , which added

Autodef automatically defined

Write assign directly or write always directly, then you can automatically define wire or reg. especially when doing top-level integration, thousands of wire connections, not at all human. Work 1000% more efficiently

Autopara auto-para instantiation

Supports both variable name substitution and automatic numeric instantiation.

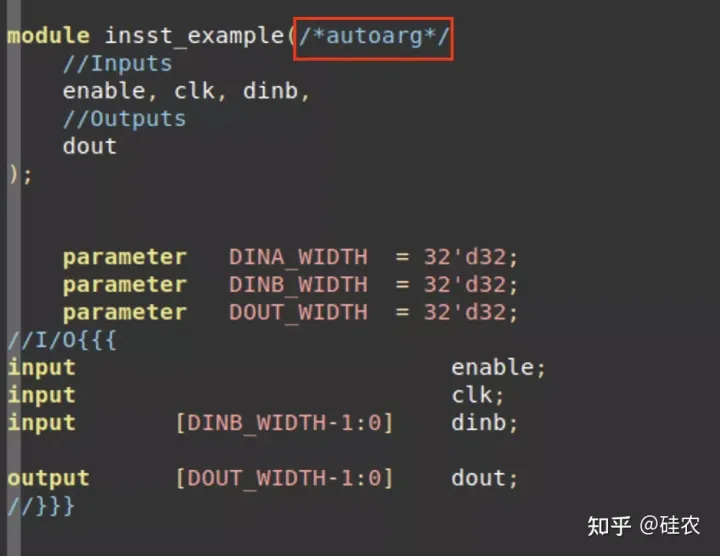

Autoarg auto-define ports

If you like the 1995 port description writing, directly help you auto-define the port, I have not written the port for years.

Support for displaying RtlTree

The above mentioned is already the most basic that can increase the efficiency of coding by 1000%, there are other more features. The header, auto-always block. Waveform comment block in code, etc.

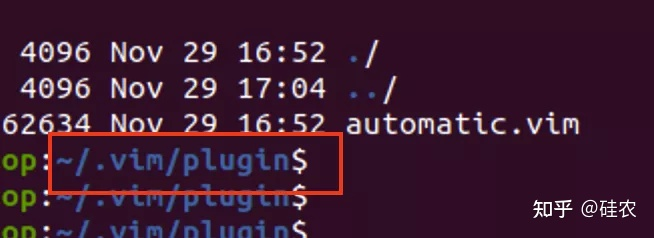

Installation and use

The installation and use method is also very simple, directly into the plugin path of the vim installation directory, if there is no such directory, create a new one. What’s more, it supports Windows, Linux and MacOs platforms. The operation is exactly the same.

So how can this be obtained? The netizen who wrote this script has all open source and is continuing to update the development. You can even develop it yourself on top of this to make a Verilog plug-in that meets your exact needs.

https://github.com/HonkW93/automatic-verilog

His personal website has a more detailed introduction and usage.

https://blog.honk.wang/posts/AutoMatic/

Finally

Listen to me, all those who use gVim have to use it, and those who don’t use gVim hope to use it sooner. Finally, I wish you all good luck in writing code!